That is,ĬPU_Instruction = Instruction_Memory 4 registers of 8 bits of information each from the Instruction Memory are read in little endian byte order and form the first 32 bits of the CPU instruction.

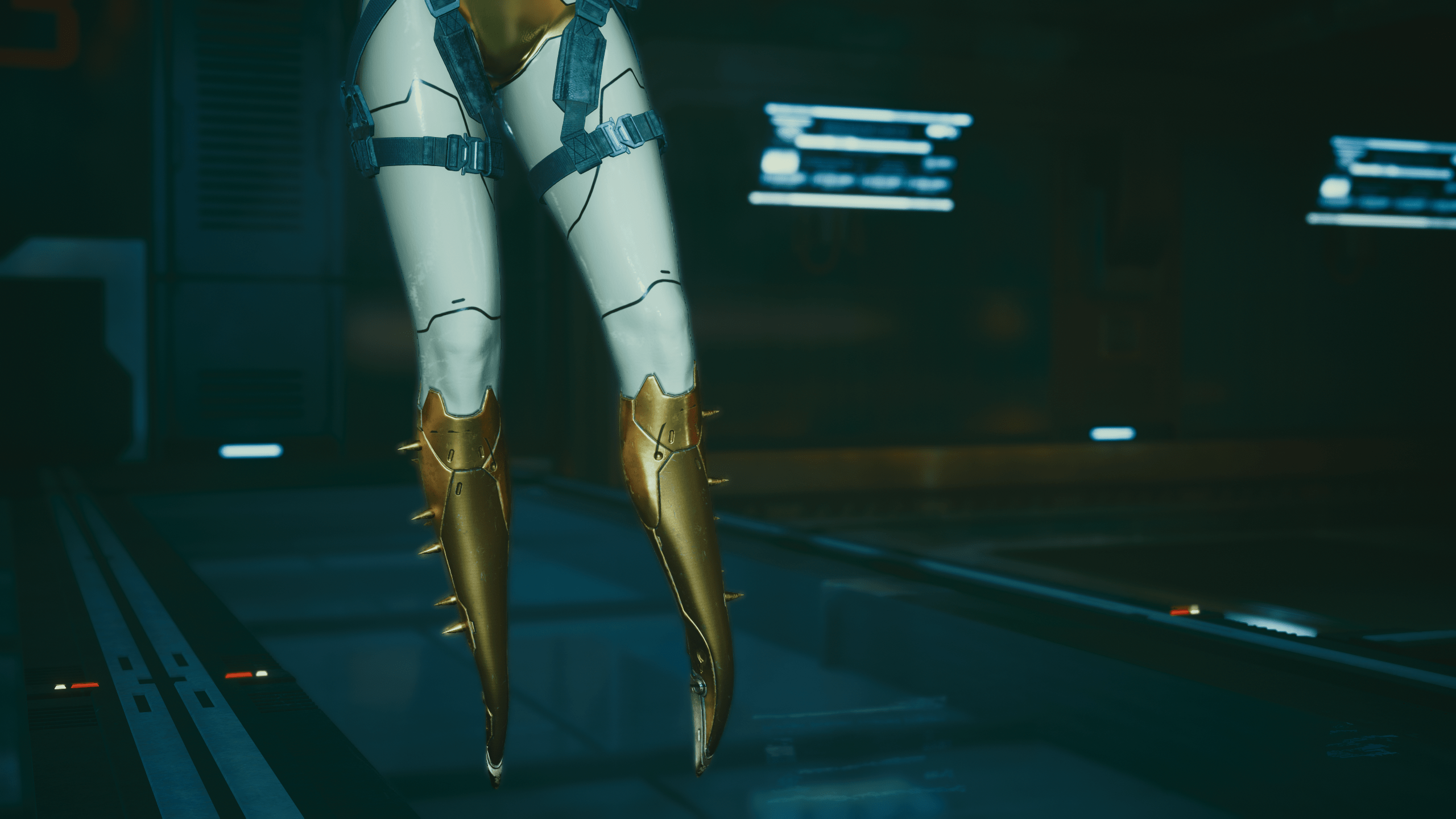

ARM AND LEG GITBOX MOD 32 BIT

The Program Counter or PC goes through the Instruction Memory and fetches a 32 bit instruction in each cycle.

ARM AND LEG GITBOX MOD 64 BITS

If the result needs to be loaded from the data memory, it can be written back to the Register module to perform any further operations.Ī CPU instruction is 64 bits wide. Depending on the type of operation performed, the result may need to be loaded from or stored to the data memory. The Registers pass the values in instruction memory to the ALU to perform operations. The Program Counter or PC reads the instructions from the instruction memory, then modifies the Register module to hold the current instruction. The CPU comprises of a Program Counter, Instruction Memory, Register module, Arithmetic Logic Unit and Data Memory. Let's start with an abstract view of the CPU. The instructions compare and branch on zero ( CBZ ) and branch ( B ).

The arithmetic-logical instructions ADD, SUB, AND and ORR.The memory-reference instructions load register unscaled ( LDUR ) and store register unscaled ( STUR ).The project implementation includes a subset of the core LEGv8 instruction set: But in LEGv8, the 32nd register or X31 is always initialized to 0.

ARM AND LEG GITBOX MOD FULL

In the full ARMv8 instruction set, register 31 is XZR in most instructionsīut the stack point ( SP ) in others. Of these 32 registers, 31 registers X0 to X30, are the general purpose registers. The 64-bit data is called a “doubleword”. LEGv8 has a 32 × 64-bit register module which is used for frequently accessed data. The LEGv8 instruction set is a subset of ARM instruction set. To favor simplicity, arithmetic operations are formed with two sources and one destination. In some cases the fact that a 64-bit core can perform certain operations quicker means that it will be more energy efficient than a 32-bit core, simply because it gets the job done faster and can then power down. In terms of energy efficiency, the use of 64-bit registers doesn’t increase the power usage. The result is that ARM’s 64-bit processors can do things quicker. This means that optimized code should be able to use the internal registers more often than memory, and that these registers can hold bigger numbers and addresses. The ARMv8 architecture has 31 general registers, each 64-bits wide. The 32-bit ARMv7 architecture had 15 general purpose registers, each 32-bits wide. Therefore more frequent use of registers for variables speeds up execution time. This means more instructions need to be executed when data is fetched from Data memory. Operating on Data memory requires loadsĪnd stores. Registers are faster to access than memory. Different formats complicate decoding, therefore keep formats as similar as possible Simplicity enables higher performance at lower cost Regularity makes implementation simpler

0 kommentar(er)

0 kommentar(er)